Qu’est-ce que l’architecture RISC et CISC avec ses avantages et ses inconvénients

CISC et RISC

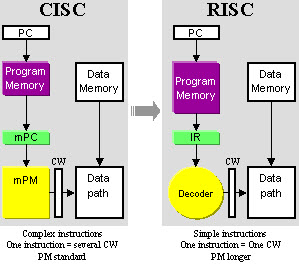

L’architecture des unités centrales de traitement exploite la capacité de travailler à partir de « l’architecture des jeux d’instructions » à l’endroit où elle a été conçue. Les conceptions architecturales des CPU sont RISC (Reduced instruction set computing) et CISC (Complex instruction set computing). Le CISC a la capacité d’exécuter des modes d’adressage ou des opérations en plusieurs étapes dans un seul jeu d’instructions. Il s’agit de la conception de l’unité centrale où une seule instruction exécute de nombreuses opérations de bas niveau. Par exemple, le stockage en mémoire, une opération arithmétique et le chargement depuis la mémoire. RISC est une stratégie de conception de CPU basée sur la perspicacité que le jeu d’instructions simplifié donne des performances plus élevées lorsqu’il est combiné avec une architecture de microprocesseur qui a la capacité d’exécuter les instructions en utilisant quelques cycles de microprocesseur par instruction.

Cet article discute de l’architecture RISC et CISC avec des diagrammes appropriés.

- Le matériel de l’Intel est qualifié de Complex Instruction Set Computer (CISC)

- Le matériel d’Apple est Reduced Instruction Set Computer (RISC).

Qu’est-ce que l’architecture RISC et CISC

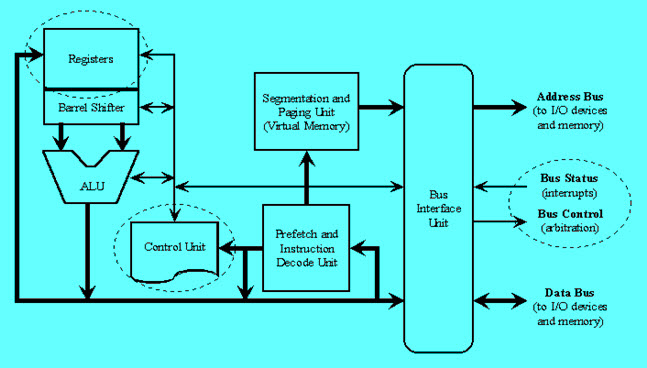

Les concepteurs de matériel inventent de nombreuses technologies & outils pour mettre en œuvre l’architecture souhaitée afin de répondre à ces besoins. L’architecture matérielle peut être mise en œuvre pour être soit spécifique au matériel, soit spécifique au logiciel, mais selon l’application, les deux sont utilisés en quantité requise. En ce qui concerne le matériel du processeur, il existe deux types de concepts pour mettre en œuvre l’architecture matérielle du processeur. Le premier est RISC et l’autre est CISC.

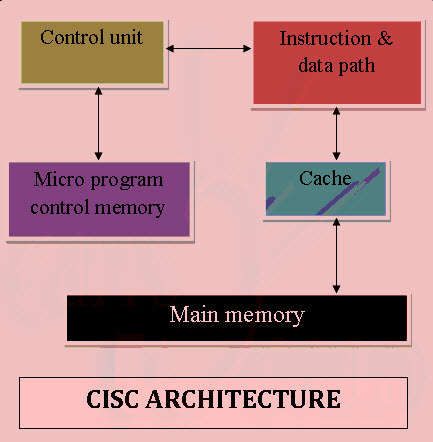

Architecture CISC

L’approche CISC tente de minimiser le nombre d’instructions par programme, en sacrifiant le nombre de cycles par instruction. Les ordinateurs basés sur l’architecture CISC sont conçus pour diminuer le coût de la mémoire. En effet, les gros programmes ont besoin de plus de stockage, ce qui augmente le coût de la mémoire et les grosses mémoires deviennent plus chères. Pour résoudre ces problèmes, le nombre d’instructions par programme peut être réduit en intégrant le nombre d’opérations dans une seule instruction, ce qui rend les instructions plus complexes.

Architecture CISC

- MUL charge deux valeurs de la mémoire dans des registres séparés en CISC.

- CISC utilise le minimum d’instructions possibles en mettant en œuvre le matériel et exécute les opérations.

- L’architecture à jeu d’instructions est un support permettant la communication entre le programmeur et le matériel. La partie d’exécution des données, la copie des données, la suppression ou l’édition sont les commandes de l’utilisateur utilisées dans le microprocesseur et avec ce microprocesseur, l’architecture de jeu d’instructions est exploitée.

- Les principaux mots-clés utilisés dans l’architecture de jeu d’instructions ci-dessus sont les suivants

Série d’instructions : Groupe d’instructions données pour exécuter le programme et elles dirigent l’ordinateur en manipulant les données. Les instructions se présentent sous la forme – Opcode (code opérationnel) et Operand. L’opcode est l’instruction appliquée pour charger et stocker des données, etc. L’opérande est un registre de mémoire où l’instruction a été appliquée.

Modes d’adressage : Les modes d’adressage correspondent à la manière dont on accède aux données. Selon le type d’instruction appliqué, les modes d’adressage sont de différents types tels que le mode direct où l’on accède directement aux données ou le mode indirect où l’on accède à l’emplacement des données. Des processeurs ayant un ISA identique peuvent être très différents dans leur organisation. Des processeurs ayant une ISA identique et une organisation presque identique ne sont toujours pas presque identiques.

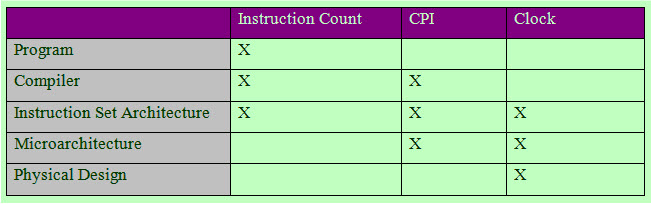

Les performances des CPU sont données par la loi fondamentale

![]()

Ainsi , Les performances du processeur dépendent du nombre d’instructions, du CPI (cycles par instruction) et du temps de cycle de l’horloge. Et tous trois sont affectés par l’architecture du jeu d’instructions.

Compte d’instructions du CPU

Ceci souligne l’importance de l’architecture du jeu d’instructions. Il existe deux architectures de jeu d’instructions prévalentes

Exemples de processeurs CISC

IBM 370/168 – Il a été introduit en l’an 1970. La conception CISC est un processeur de 32 bits et quatre registres à virgule flottante de 64 bits.

VAX 11/780 – La conception CISC est un processeur de 32 bits et il supporte de nombreux nombres de modes d’adressage et d’instructions machine qui est de Digital Equipment Corporation.

Intel 80486 – Il a été lancé dans l’année 1989 et c’est un processeur CISC, qui a des instructions variant de longueur de 1 à 11 et il aura 235 instructions.

CHARACTÉRISTIQUES DE L’ARCHITECTURE CISC

- La logique de décodage des instructions sera complexe.

- Une instruction est nécessaire pour supporter plusieurs modes d’adressage.

- Moins d’espace sur la puce est suffisant pour les registres à usage général pour les instructions qui sont 0opérées directement sur la mémoire.

- Diverses conceptions CISC sont mises en place deux registres spéciaux pour le pointeur de pile, la gestion des interruptions, etc.

- MUL est qualifié d' »instruction complexe » et nécessite le programmeur pour le stockage des fonctions.

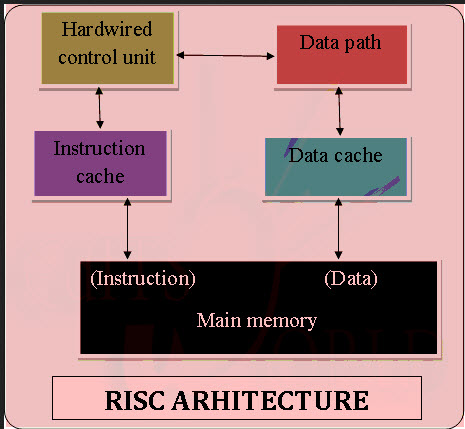

Architecture RISC

RISC (Reduced Instruction Set Computer) est utilisé dans les appareils portables en raison de son efficacité énergétique. Par exemple, l’Apple iPod et la Nintendo DS. RISC est un type d’architecture de microprocesseur qui utilise un ensemble d’instructions hautement optimisées. Le RISC fait l’inverse, en réduisant les cycles par instruction au prix du nombre d’instructions par programme Le pipelage est l’une des caractéristiques uniques du RISC. Il est réalisé en superposant l’exécution de plusieurs instructions à la manière d’un pipeline. Il présente un avantage de performance élevé par rapport au CISC.

Architecture RISC

Les processeurs RISC. prennent des instructions simples et sont exécutés dans un cycle d’horloge

Caractéristiques de l’architecture RISC

- Les instructions simples sont utilisées dans l’architecture RISC.

- RISC aide et supporte quelques types de données simples et synthétise des types de données complexes.

- RISC utilise des modes d’adressage simples et des instructions de longueur fixe pour le pipelining.

- RISC permet d’utiliser n’importe quel registre dans n’importe quel contexte.

- Temps d’exécution d’un cycle

- La quantité de travail qu’un ordinateur peut effectuer est réduite en séparant les instructions « LOAD » et « STORE ».

- RISC contient un grand nombre de registres afin d’éviter un nombre varié d’interactions avec la mémoire.

- En RISC, le Pipelining est facile car l’exécution de toutes les instructions se fera dans un intervalle de temps uniforme c’est-à-dire en un clic.

- En RISC, plus de RAM est nécessaire pour stocker les instructions de niveau assemblage.

- Les instructions réduites nécessitent un nombre moins important de transistors en RISC.

- Le RISC utilise le modèle de mémoire de Harvard signifie que c’est une architecture de Harvard.

- Un compilateur est utilisé pour effectuer l’opération de conversion signifie convertir une déclaration en langage de haut niveau dans le code de sa forme.

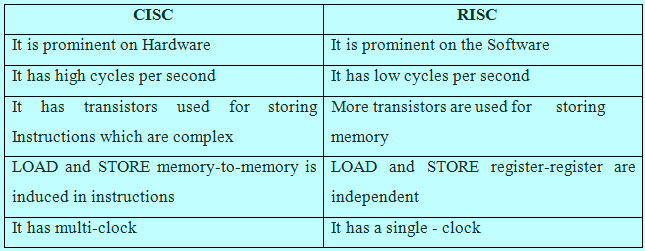

RISC & Comparaison entre CISC

Comparaison entre CISC & RISC

L’instruction MUL est divisée en trois instructions

« LOAD » – déplace des données de la banque de mémoire vers un registre

« PROD » – trouve le produit de deux opérandes situés dans les registres

« STORE » – déplace des données d’un registre vers les banques de mémoire

La principale différence entre RISC et CISC est le nombre d’instructions et sa complexité.

RISC Vs CISC

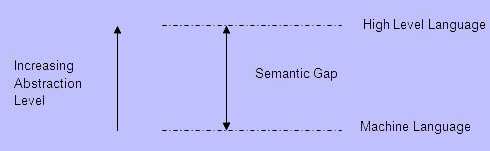

L’écart sémantique

Les deux architectures RISC et CISC ont été développées pour tenter de couvrir l’écart sémantique.

L’écart sémantique

Dans le but d’améliorer l’efficacité du développement de logiciels, plusieurs langages de programmation puissants ont vu le jour, à savoir , Ada, C, C++, Java, etc. Ils offrent un haut niveau d’abstraction, de concision et de puissance. Ces langages offrent un haut niveau d’abstraction, de concision et de puissance. Par cette évolution, le fossé sémantique se creuse. Pour permettre une compilation efficace des programmes en langage de haut niveau, les conceptions CISC et RISC sont les deux options possibles.

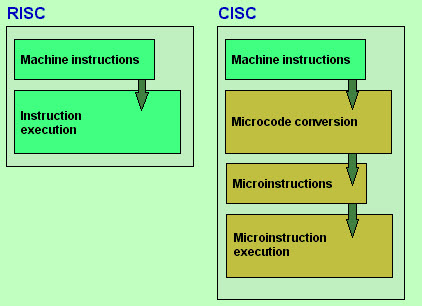

Les conceptions CISC impliquent des architectures très complexes, comprenant un grand nombre d’instructions et de modes d’adressage, tandis que les conceptions RISC impliquent un jeu d’instructions simplifié et l’adaptent aux besoins réels des programmes utilisateurs.

CISC et conception RISC

Multiplication de deux nombres en mémoire

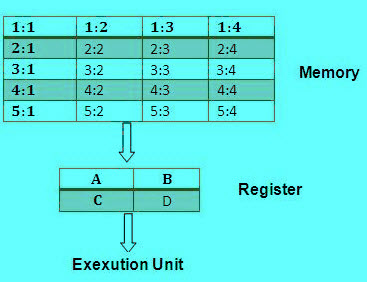

Si la mémoire principale est divisée en zones qui sont numérotées de la rangée1 :colonne 1 à ligne 5 :colonne 4. Les données sont chargées dans l’un des quatre registres (A, B, C ou D). Pour trouver la multiplication de deux nombres- Un stocké dans l’emplacement 1:3 et l’autre stocké dans l’emplacement 4:2 et stocker en retour le résultat dans 1:3.

Multiplication de deux nombres

Les avantages et les inconvénients de RISC et de… CISC

Les avantages de l’architecture RISC

- L’architecture RISC(Reduced instruction set computing)possède un ensemble d’instructions, ainsi les compilateurs de langage de haut niveau peuvent produire un code plus efficace

- Elle permet une liberté d’utilisation de l’espace sur les microprocesseurs du fait de sa simplicité.

- De nombreux processeurs RISC utilisent les registres pour passer les arguments et contenir les variables locales.

- Les fonctions RISC n’utilisent que quelques paramètres, et les processeurs RISC ne peuvent pas utiliser les instructions d’appel, et donc, utilisent une instruction de longueur fixe qui est facile à mettre en pipeline.

- La vitesse de l’opération peut être maximisée et le temps d’exécution peut être minimisé.

Très peu de formats d’instruction, quelques nombres d’instructions et quelques modes d’adressage sont nécessaires.

Les inconvénients de l’architecture RISC

- Principalement, les performances des processeurs RISC dépendent du programmeur ou du compilateur car les connaissances du compilateur jouent un rôle essentiel lors de la transformation du code CISC en code RISC

- Lors de la réorganisation du code CISC en code RISC, appelée expansion de code, la taille augmentera. Et, la qualité de cette expansion de code dépendra à nouveau du compilateur, et aussi du jeu d’instructions de la machine.

- Le cache de premier niveau des processeurs RISC est aussi un inconvénient du RISC, dans lequel ces processeurs ont de grands caches mémoire sur la puce elle-même. Pour alimenter les instructions, ils nécessitent des systèmes de mémoire très rapides.

Avantages de l’architecture CISC

- La microprogrammation est facile à mettre en œuvre en langage d’assemblage, et moins coûteuse que le câblage en dur d’une unité de commande.

- La facilité de microcodage de nouvelles instructions a permis aux concepteurs de rendre les machines CISC compatibles vers le haut :

- A mesure que chaque instruction devenait plus aboutie, moins d’instructions pouvaient être utilisées pour réaliser une tâche donnée.

Inconvénients de l’architecture CISC

- Les performances de la machine ralentissent en raison du temps d’horloge pris par les différentes instructions. temps d’horloge pris par les différentes instructions sera dissemblable

- Seul 20% des instructions existantes est utilisé dans un événement de programmation typique, même s’il existe en réalité diverses instructions spécialisées qui ne sont même pas utilisées fréquemment.

- Les codes conditionnels sont mis en place par les instructions CISC comme un effet secondaire de chaque instruction qui prend du temps pour cette mise en place – et, comme l’instruction suivante change les bits de code conditionnel – ainsi, le compilateur doit examiner les bits de code conditionnel avant que cela ne se produise.

Ainsi, cet article traite des architectures RISC et CISC ; des caractéristiques de l’architecture des processeurs RISC et CISC ; des avantages et des inconvénients des RISC et CISC, et de la comparaison entre les architectures RISC et CISC . Pour plus d’informations sur les architectures RISC et CISC, ou sur des projets d’électricité et d’électronique, veuillez consulter le lien www.edgefxkits.com. Voici une question pour vous, quels sont les derniers processeurs RISC et CISC ?

Photo Credits:

- CISc and RISC Design by dickinson

- RISC Vs CISC by ydcdn

- CISC architecture by editsworld

.