Was ist RISC- und CISC-Architektur mit Vor- und Nachteilen

CISC und RISC

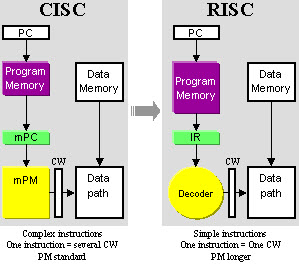

Die Architektur der Central Processing Unit (CPU) hat die Fähigkeit, von der „Instruction Set Architecture“ aus zu arbeiten, für die sie entworfen wurde. Die Architekturen der CPU sind RISC (Reduced instruction set computing) und CISC (Complex instruction set computing). CISC hat die Fähigkeit, Adressierungsmodi oder mehrstufige Operationen innerhalb eines Befehlssatzes auszuführen. Es ist das Design der CPU, bei dem ein Befehl viele Low-Level-Operationen ausführt. Zum Beispiel die Speicherung im Speicher, eine arithmetische Operation und das Laden aus dem Speicher. RISC ist eine CPU-Entwurfsstrategie, die auf der Erkenntnis beruht, dass ein vereinfachter Befehlssatz eine höhere Leistung ergibt, wenn er mit einer Mikroprozessorarchitektur kombiniert wird, die in der Lage ist, die Befehle unter Verwendung einiger Mikroprozessorzyklen pro Befehl auszuführen.

Dieser Artikel behandelt die RISC- und CISC-Architektur mit geeigneten Diagrammen.

- Die Hardware von Intel wird als Complex Instruction Set Computer (CISC)

- Apple-Hardware ist Reduced Instruction Set Computer (RISC).

Was ist RISC- und CISC-Architektur

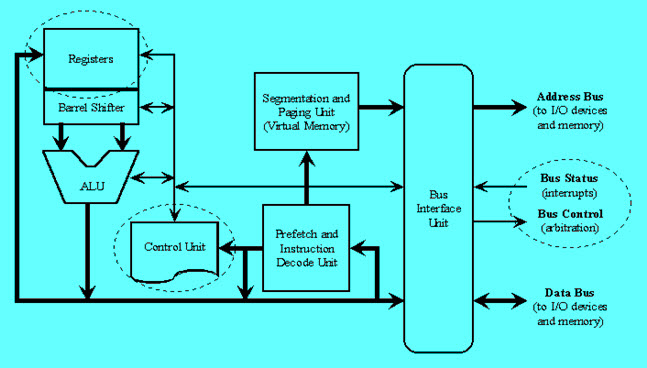

Hardware-Designer erfinden zahlreiche Technologien &Tools, um die gewünschte Architektur zu implementieren, um diese Anforderungen zu erfüllen. Die Hardware-Architektur kann entweder hardwarespezifisch oder softwarespezifisch implementiert werden, aber je nach Anwendung wird beides in der erforderlichen Menge verwendet. Was die Prozessor-Hardware betrifft, so gibt es 2 Arten von Konzepten zur Implementierung der Prozessor-Hardware-Architektur. Das eine ist RISC und das andere ist CISC.

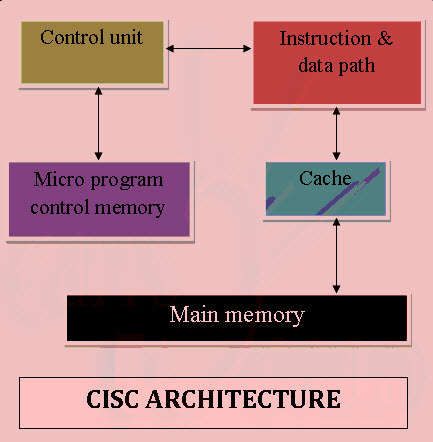

CISC-Architektur

Der CISC-Ansatz versucht, die Anzahl der Instruktionen pro Programm zu minimieren und opfert dafür die Anzahl der Zyklen pro Instruktion. Computer, die auf der CISC-Architektur basieren, sind darauf ausgelegt, die Speicherkosten zu senken. Denn, die großen Programme benötigen mehr Speicher, wodurch die Speicherkosten steigen und großer Speicher teurer wird. Um diese Probleme zu lösen, kann die Anzahl der Anweisungen pro Programm reduziert werden, indem die Anzahl der Operationen in eine einzige Anweisung eingebettet wird, wodurch die Anweisungen komplexer werden.

CISC-Architektur

- MUL lädt im CISC zwei Werte aus dem Speicher in separate Register.

- CISC verwendet ein Minimum an Anweisungen, indem es die Hardware implementiert und Operationen ausführt.

- Die Befehlssatzarchitektur ist ein Medium, das die Kommunikation zwischen dem Programmierer und der Hardware ermöglicht. Der Teil der Datenausführung, das Kopieren von Daten, das Löschen oder Editieren sind die Benutzerbefehle, die im Mikroprozessor verwendet werden, und mit diesem Mikroprozessor wird die Instruction Set Architecture betrieben.

- Die wichtigsten Schlüsselwörter, die in der obigen Instruction Set Architecture verwendet werden, sind wie folgt

Instruction Set: Gruppe von Anweisungen, die zur Ausführung des Programms gegeben werden und die den Computer durch Manipulation der Daten steuern. Befehle sind in der Form – Opcode (Operationscode) und Operand. Dabei ist der Opcode die Anweisung, die zum Laden und Speichern von Daten usw. verwendet wird. Der Operand ist ein Speicherregister, auf das der Befehl angewendet wird.

Adressierungsmodi: Adressierungsmodi sind die Art und Weise, wie auf die Daten zugegriffen wird. Abhängig von der Art der angewendeten Instruktion gibt es verschiedene Adressierungsmodi, wie z. B. den direkten Modus, bei dem direkt auf die Daten zugegriffen wird, oder den indirekten Modus, bei dem auf den Ort der Daten zugegriffen wird. Prozessoren mit identischem ISA können sehr unterschiedlich organisiert sein. Prozessoren mit identischem ISA und nahezu identischer Organisation sind immer noch nicht nahezu identisch.

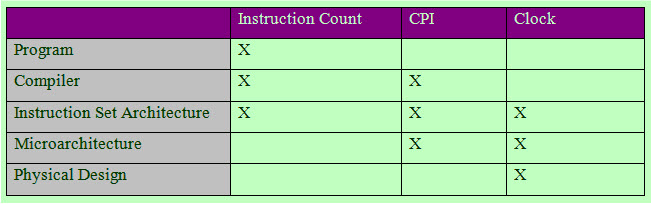

CPU-Leistung ist durch das Grundgesetz gegeben

![]()

Das heißt, Die CPU-Leistung ist abhängig von der Anzahl der Instruktionen, dem CPI (Zyklen pro Instruktion) und der Taktzykluszeit. Und alle drei werden von der Befehlssatzarchitektur beeinflusst.

Befehlsanzahl der CPU

Dies unterstreicht die Bedeutung der Befehlssatzarchitektur. Es gibt zwei vorherrschende Befehlssatzarchitekturen

Beispiele für CISC-Prozessoren

IBM 370/168 – Er wurde im Jahr 1970 eingeführt. CISC-Design ist ein 32-Bit-Prozessor und vier 64-Bit-Gleitkommaregister.

VAX 11/780 – CISC-Design ist ein 32-Bit-Prozessor und unterstützt viele Adressierungsmodi und Maschinenbefehle, der von Digital Equipment Corporation ist.

Intel 80486 – Er wurde im Jahr 1989 auf den Markt gebracht und ist ein CISC-Prozessor, der Befehle mit Längen von 1 bis 11 hat und über 235 Befehle verfügt.

CHARAKTERISTIK DER CISC-ARCHITEKTUR

- Die Logik zur Befehlsdekodierung wird komplex sein.

- Eine Anweisung ist erforderlich, um mehrere Adressierungsmodi zu unterstützen.

- Für die Befehle, die direkt auf den Speicher 0operiert werden, steht weniger Chipplatz für Allzweckregister zur Verfügung.

- Viele CISC-Designs richten zwei Spezialregister für den Stack-Pointer, die Behandlung von Interrupts usw. ein.

- MUL wird als „komplexe Instruktion“ bezeichnet und erfordert den Programmierer für die Speicherung von Funktionen.

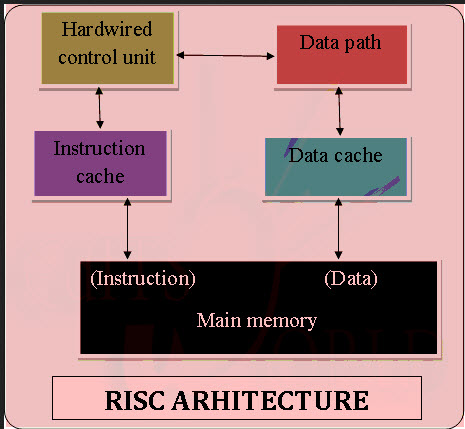

RISC-Architektur

RISC (Reduced Instruction Set Computer) wird wegen seiner Leistungseffizienz in tragbaren Geräten eingesetzt. Zum Beispiel im Apple iPod und Nintendo DS. RISC ist eine Art von Mikroprozessor-Architektur, die einen hochoptimierten Satz von Anweisungen verwendet. RISC macht das Gegenteil und reduziert die Zyklen pro Anweisung auf Kosten der Anzahl der Anweisungen pro Programm Pipelining ist eines der einzigartigen Merkmale von RISC. Es wird durch Überlappung der Ausführung mehrerer Anweisungen in einer Pipeline durchgeführt. Es hat einen hohen Leistungsvorteil gegenüber CISC.

RISC Architektur

RISC Prozessoren nehmen einfache Instruktionen und werden innerhalb eines Taktzyklus ausgeführt

RISC ARCHITEKTUR MERKMALE

- In der RISC-Architektur werden einfache Instruktionen verwendet.

- RISC hilft und unterstützt wenige einfache Datentypen und synthetisiert komplexe Datentypen.

- RISC verwendet einfache Adressierungsmodi und Anweisungen mit fester Länge für Pipelining.

- RISC erlaubt die Verwendung jedes Registers in jedem Kontext.

- Ein-Zyklus-Ausführungszeit

- Der Arbeitsaufwand eines Computers wird durch die Trennung von „LOAD“- und „STORE“-Befehlen reduziert.

- RISC enthält eine große Anzahl von Registern, um verschiedene Anzahlen von Interaktionen mit dem Speicher zu vermeiden.

- In RISC ist Pipelining einfach, da die Ausführung aller Befehle in einem einheitlichen Zeitintervall, d.h. in einem Klick, erfolgt.

- In RISC wird mehr RAM benötigt, um Befehle auf Assembler-Ebene zu speichern.

- Reduzierte Anweisungen benötigen eine geringere Anzahl von Transistoren in RISC.

- RISC verwendet das Harvard-Speichermodell, d.h. es ist eine Harvard-Architektur.

- Ein Compiler wird verwendet, um die Konvertierungsoperation durchzuführen, d.h. um eine Hochsprachenanweisung in den Code seiner Form umzuwandeln.

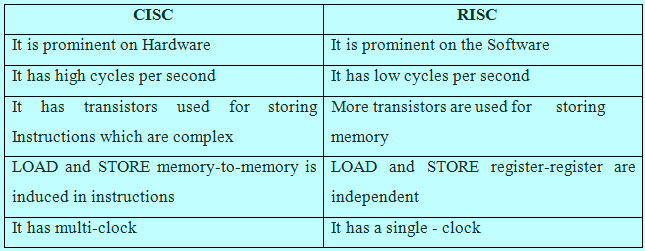

RISC & CISC Vergleich

Vergleich zwischen CISC & RISC

Der Mul-Befehl ist in drei Anweisungen unterteilt

„LOAD“ – verschiebt Daten aus der Speicherbank in ein Register

„PROD“ – findet das Produkt zweier Operanden, die sich in den Registern befinden

„STORE“ – verschiebt Daten aus einem Register in die Speicherbänke

Der Hauptunterschied zwischen RISC und CISC ist die Anzahl der Befehle und deren Komplexität.

RISC Vs CISC

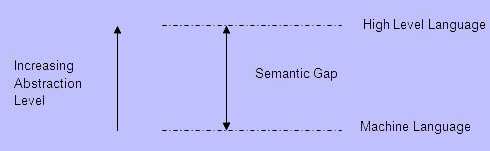

SEMANTISCHE LÜCKE

Beide Architekturen, RISC und CISC, wurden als Versuch entwickelt, die semantische Lücke zu schließen.

Semantische Lücke

Mit dem Ziel, die Effizienz der Softwareentwicklung zu verbessern, sind mehrere mächtige Programmiersprachen entstanden, nämlich, Ada, C, C++, Java, etc. Sie bieten ein hohes Maß an Abstraktion, Prägnanz und Mächtigkeit. Durch diese Entwicklung wächst die semantische Lücke. Um eine effiziente Kompilierung von Hochsprachenprogrammen zu ermöglichen, sind CISC- und RISC-Entwürfe die beiden Optionen.

CISC-Entwürfe beinhalten sehr komplexe Architekturen, einschließlich einer großen Anzahl von Befehlen und Adressierungsmodi, während RISC-Entwürfe einen vereinfachten Befehlssatz beinhalten und diesen an die realen Anforderungen der Anwenderprogramme anpassen.

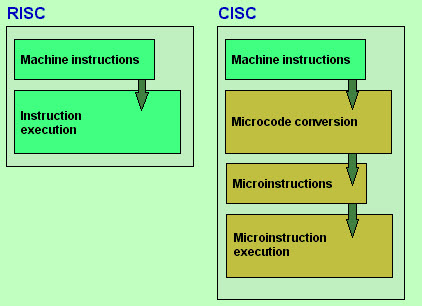

CISC- und RISC-Design

Multiplikation zweier Zahlen im Speicher

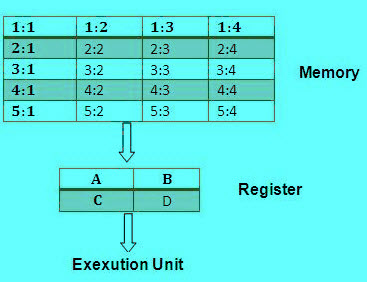

Wenn der Hauptspeicher in Bereiche unterteilt ist, die von Zeile1:Spalte1 bis Zeile5 :Spalte4. Die Daten werden in eines von vier Registern (A, B, C, oder D) geladen. Um die Multiplikation zweier Zahlen zu finden, wird die eine in Speicherplatz 1:3 und die andere in Speicherplatz 4:2 gespeichert und das Ergebnis in 1:3 zurückgespeichert.

Multiplikation von zwei Zahlen

Die Vor- und Nachteile von RISC und CISC

Die Vorteile der RISC-Architektur

- Die RISC(Reduced instruction set computing)-Architektur hat einen Satz von Anweisungen, so dass Hochsprachen-Compiler effizienteren Code erzeugen können

- Es ermöglicht die freie Nutzung des Platzes auf Mikroprozessoren aufgrund seiner Einfachheit.

- Viele RISC-Prozessoren verwenden die Register zur Übergabe von Argumenten und zum Halten der lokalen Variablen.

- RISC-Funktionen verwenden nur wenige Parameter, und die RISC-Prozessoren können die Aufrufanweisungen nicht verwenden und verwenden daher eine Anweisung mit fester Länge, die leicht in der Pipeline zu verarbeiten ist.

- Die Geschwindigkeit der Operation kann maximiert und die Ausführungszeit minimiert werden.

Eine sehr geringe Anzahl von Befehlsformaten, eine geringe Anzahl von Anweisungen und wenige Adressierungsmodi werden benötigt.

Die Nachteile der RISC-Architektur

- Vor allem, hängt die Leistung der RISC-Prozessoren vom Programmierer oder Compiler ab, da das Wissen des Compilers eine wichtige Rolle spielt, wenn der CISC-Code in einen RISC-Code umgewandelt wird

- Während der Umstellung des CISC-Codes auf einen RISC-Code, die als Code-Erweiterung bezeichnet wird, wird die Größe erhöht. Und die Qualität dieser Code-Erweiterung hängt wiederum vom Compiler und auch vom Befehlssatz der Maschine ab.

- Der First-Level-Cache der RISC-Prozessoren ist auch ein Nachteil des RISC, bei dem diese Prozessoren große Speicher-Caches auf dem Chip selbst haben. Für die Zuführung der Befehle benötigen sie sehr schnelle Speichersysteme.

Vorteile der CISC-Architektur

- Die Mikroprogrammierung ist einfach in Assembler zu implementieren und weniger teuer als die feste Verdrahtung eines Steuergeräts.

- Die einfache Mikrocodierung neuer Befehle ermöglichte es den Entwicklern, CISC-Maschinen aufwärtskompatibel zu machen:

- Wenn jeder Befehl immer besser wird, können weniger Befehle verwendet werden, um eine bestimmte Aufgabe zu implementieren.

Nachteile der CISC-Architektur

- Die Leistung der Maschine verlangsamt sich durch die Menge der Taktzeit, die von verschiedenen Instruktionen benötigt wird, unterschiedlich ist

- Nur 20% der vorhandenen Instruktionen werden in einem typischen Programmiervorgang verwendet, obwohl es in der Realität diverse spezialisierte Anweisungen gibt, die nicht einmal häufig verwendet werden.

- Die Conditional Codes werden von den CISC-Befehlen als Nebeneffekt jeder Anweisung gesetzt, was Zeit für dieses Setzen benötigt – und da die nachfolgende Anweisung die Condition Code Bits ändert, muss der Compiler die Condition Code Bits untersuchen, bevor dies geschieht.

Dieser Artikel behandelt also die RISC- und CISC-Architekturen, die Merkmale der RISC- und CISC-Prozessorarchitektur, die Vor- und Nachteile von RISC und CISC und den Vergleich zwischen RISC- und CISC-Architekturen. Für weitere Informationen zu den RISC- und CISC-Architekturen oder zu Elektro- und Elektronikprojekten besuchen Sie bitte den Link www.edgefxkits.com. Hier ist eine Frage für Sie, was sind die neuesten RISC- und CISC-Prozessoren?

Photo Credits:

- CISc und RISC Design von dickinson

- RISC Vs CISC von ydcdn

- CISC Architektur von editsworld