O que é a Arquitectura RISC e CISC com Vantagens e Desvantagens

CISC e RISC

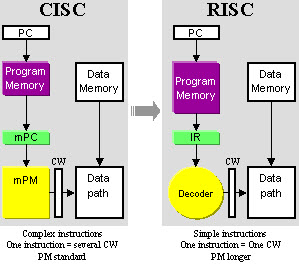

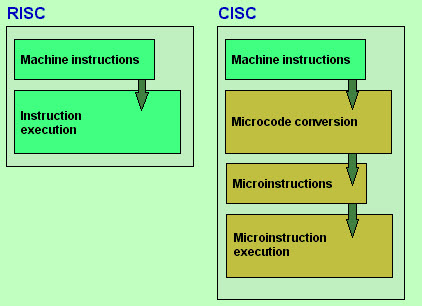

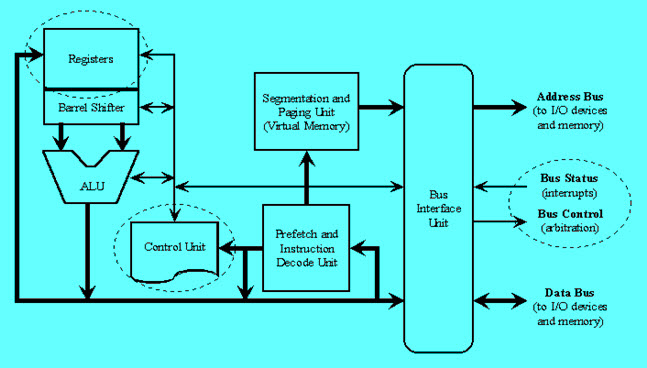

Central Processing Unit Architecture opera a capacidade de trabalhar desde “Instruction Set Architecture” até ao local onde foi concebido. Os desenhos arquitectónicos da CPU são RISC (Reduced instruction set computing) e CISC (Complex instruction set computing). A CISC tem a capacidade de executar modos de endereçamento ou operações de múltiplos passos dentro de um conjunto de instruções. É o desenho da CPU onde uma instrução executa muitas operações de baixo nível. Por exemplo, armazenamento de memória, uma operação aritmética e carregamento a partir da memória. RISC é uma estratégia de concepção da CPU baseada na percepção de que um conjunto simplificado de instruções proporciona um desempenho superior quando combinado com uma arquitectura de microprocessador que tem a capacidade de executar as instruções utilizando alguns ciclos de microprocessador por instrução.

Este artigo discute sobre a arquitectura RISC e CISC com diagramas adequados.

- Hardware da Intel é denominado Computador de Conjunto de Instruções Complexas (CISC)

- Aplicar hardware é Computador de Conjunto de Instruções Reduzidas (RISC).

O que é RISC e Arquitectura CISC

Desenhadores de hardware inventam numerosas tecnologias & ferramentas para implementar a arquitectura desejada a fim de satisfazer estas necessidades. A arquitectura de hardware pode ser implementada para ser específica de hardware ou de software, mas de acordo com a aplicação, ambas são utilizadas na quantidade requerida. No que diz respeito ao hardware do processador, existem 2 tipos de conceitos para implementar a arquitectura de hardware do processador. O primeiro é RISC e o outro é CISC.

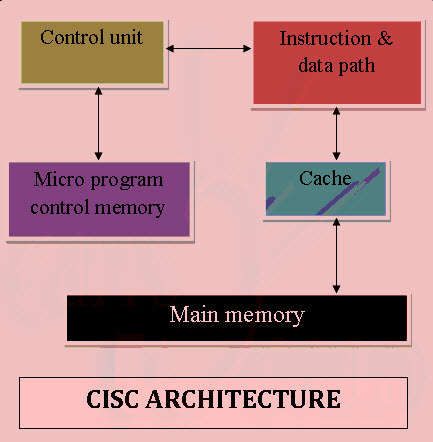

CISC Architecture

A abordagem CISC tenta minimizar o número de instruções por programa, sacrificando o número de ciclos por instrução. Os computadores baseados na arquitectura CISC são concebidos para diminuir o custo da memória. Porque os programas grandes precisam de mais armazenamento, aumentando assim o custo da memória e a memória grande torna-se mais cara. Para resolver estes problemas, o número de instruções por programa pode ser reduzido através da incorporação do número de operações numa única instrução, tornando assim as instruções mais complexas.

p>CISC Architecture

p>CISC Architecture - MUL carrega dois valores da memória em registos separados no CISC.

- CISC utiliza o mínimo de instruções possíveis ao implementar hardware e executa operações.

- Instruction Set Architecture é um meio para permitir a comunicação entre o programador e o hardware. Parte da execução de dados, cópia de dados, eliminação ou edição são os comandos do utilizador utilizados no microprocessador e com este microprocessador é operada a arquitectura do Conjunto de Instruções.

- As principais palavras-chave utilizadas na Arquitectura do Conjunto de Instruções acima são as seguintes

Instruction Set: Grupo de instruções dadas para executar o programa e elas dirigem o computador através da manipulação dos dados. As instruções estão na forma – Opcode (código operacional) e Operand. Onde, opcode é a instrução aplicada para carregar e armazenar dados, etc. O operando é um registo de memória onde a instrução aplicada.

Modos de endereçamento: Os modos de endereçamento são a forma em que os dados são acedidos. Dependendo do tipo de instrução aplicada, os modos de endereçamento são de vários tipos, tais como o modo directo onde os dados directos são acedidos ou o modo indirecto onde a localização dos dados é acedida. Os processadores com ISA idênticos podem ser muito diferentes na organização. Os processadores com ISA idênticos e com organização quase idêntica ainda não são quase idênticos.

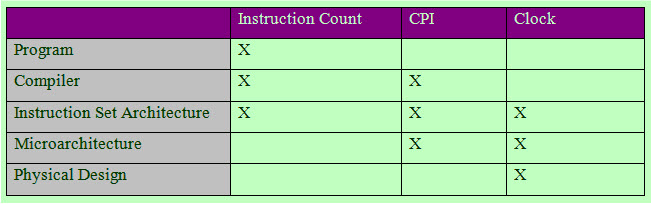

desempenho da CPU é dado pela lei fundamental

![]() br>>br>Thus, O desempenho da CPU depende da Contagem de Instrução, CPI (Ciclos por instrução) e do tempo de ciclo do Relógio. E todos os três são afectados pela arquitectura do conjunto de instruções.

br>>br>Thus, O desempenho da CPU depende da Contagem de Instrução, CPI (Ciclos por instrução) e do tempo de ciclo do Relógio. E todos os três são afectados pela arquitectura do conjunto de instruções.

Contagem de instruções da CPU

Este facto sublinha a importância da arquitectura do conjunto de instruções. Existem duas arquitecturas de conjuntos de instruções predominantes

Exemplos de PROCESSORES CISC

IBM 370/168 – Foi introduzido no ano de 1970. CISC design é um processador de 32 bits e quatro registos de 64 bits de ponto flutuante.

VAX 11/780 – CISC design é um processador de 32 bits e suporta muitos números de modos de endereçamento e instruções de máquina que é da Digital Equipment Corporation.

Intel 80486 – Foi lançado no ano de 1989 e é um processador CISC, que tem instruções de comprimento variável de 1 a 11 e terá 235 instruções.

CHARACTERISTICS OF CISC ARCHITECTURE

- Lógica de descodificação de instruções será Complexa.

- É necessária uma instrução para suportar modos de endereçamento múltiplos.

- Sem espaço no chip é suficiente para registos de uso geral para as instruções que são 0 operadas directamente na memória.

- Diversos desenhos CISC são configurados dois registos especiais para o ponteiro da pilha, interrupções de manuseamento, etc.

- MUL é referido como uma “instrução complexa” e requer o programador para armazenar funções.

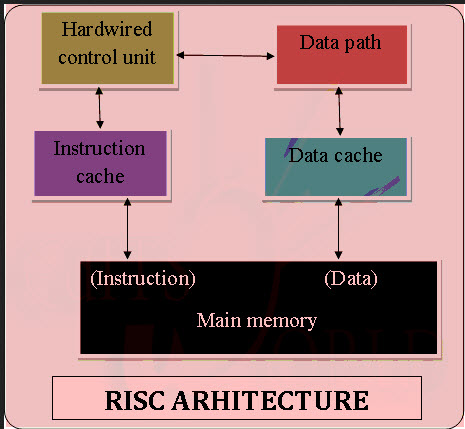

RISC Architecture

RISC (Reduced Instruction Set Computer) é utilizado em dispositivos portáteis devido à sua eficiência energética. Por exemplo, iPod Apple e Nintendo DS. O RISC é um tipo de arquitectura de microprocessador que utiliza um conjunto de instruções altamente optimizado. RISC faz o oposto, reduzindo os ciclos por instrução ao custo do número de instruções por programa Pipelining é uma das características únicas de RISC. É executada através da sobreposição da execução de várias instruções de uma forma gasosa. Tem uma vantagem de alto desempenho em relação ao CISC.

Arquitectura RISC

processadores RISC tomam instruções simples e são executadas dentro de um ciclo de relógio

CARACTERÍSTICAS DE ARQUITECTURA RISC

- Instruções simples são usadas na arquitectura RISC.

- RISC ajuda e suporta poucos tipos de dados simples e sintetiza tipos de dados complexos.

- RISC utiliza modos de endereçamento simples e instruções de comprimento fixo para pipelinagem.

- RISC permite a utilização de qualquer registo em qualquer contexto.

- Tempo de Execução de um Ciclo

- A quantidade de trabalho que um computador pode realizar é reduzida pela separação das instruções “LOAD” e “STORE”.

- RISC contém Grande Número de Registos, a fim de evitar vários números de interacções com a memória.

- Em RISC, Pipelining é fácil pois a execução de todas as instruções será feita num intervalo de tempo uniforme, ou seja, um clique.

- Em RISC, é necessária mais RAM para armazenar instruções de nível de montagem.

- Instruções reduzidas precisam de menos transistores em RISC.

- RISC usa modelo de memória de Harvard significa que é Arquitectura de Harvard.

- Um compilador é utilizado para realizar a operação de conversão significa converter uma declaração de linguagem de alto nível para o código da sua forma.

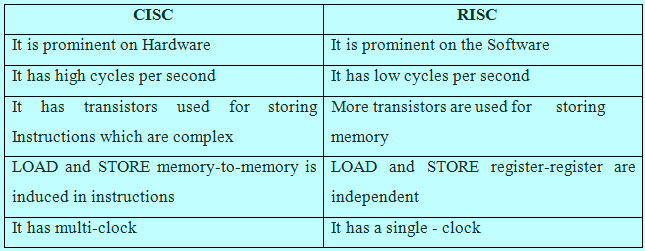

RISC & Comparação CISC

Comparação entre CISC & RISC

Instrução MUL é dividida em três instruções

“LOAD” – move dados do banco de memória para um registo

“PROD” – encontra produto de dois operandos localizados dentro dos registos

“STORE” – move dados de um registo para os bancos de memória

A principal diferença entre RISC e CISC é o número de instruções e a sua complexidade.

RISC Vs CISC

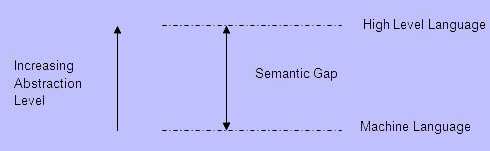

SEMANTIC GAP

As arquitecturas RISC e CISC foram desenvolvidas como uma tentativa de cobrir a lacuna semântica.

p>Gap semântico

p>Gap semântico Com o objectivo de melhorar a eficiência do desenvolvimento de software, surgiram várias linguagens de programação poderosas, a saber Ada, C, C++, Java, etc. Elas proporcionam um elevado nível de abstracção, concisão e poder. Com esta evolução, o fosso semântico cresce. Para permitir a compilação eficiente de programas de linguagem de alto nível, os desenhos CISC e RISC são as duas opções.

Desenhos CISC envolvem arquitecturas muito complexas, incluindo um grande número de instruções e modos de endereçamento, enquanto que os desenhos RISC envolvem um conjunto simplificado de instruções e adaptam-nas aos requisitos reais dos programas dos utilizadores.

p>CISC e RISC Design

p>CISC e RISC Design Multiplicação de dois Números em Memória

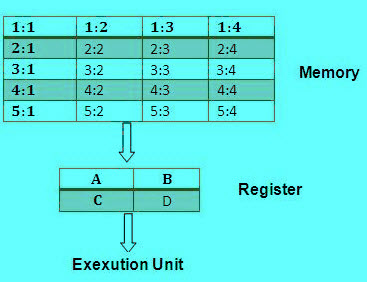

Se a memória principal estiver dividida em áreas numeradas a partir da linha 1:coluna 1 para a linha 5: coluna 4. Os dados são carregados num de quatro registos (A, B, C, ou D). Para encontrar multiplicação de dois números – Um armazenado no local 1:3 e outro armazenado no local 4:2 e armazenar de volta resulta em 1:3.

p>Multiplicação de Dois Números

p>Multiplicação de Dois Números As Vantagens e Desvantagens do RISC e CISC

The Advantages of RISC architecture

- RISC(Reduced instruction set computing)architecture has a set of instructions, para que os compiladores de linguagem de alto nível possam produzir código mais eficiente

- Permite a liberdade de utilizar o espaço em microprocessadores devido à sua simplicidade.

- Muitos processadores RISC utilizam os registos para passar argumentos e manter as variáveis locais.

- As funções RISC utilizam apenas alguns parâmetros, e os processadores RISC não podem utilizar as instruções de chamada, e portanto, utilizam uma instrução de comprimento fixo que é fácil de canalizar.

- A velocidade da operação pode ser maximizada e o tempo de execução pode ser minimizado.

Muito menos formatos de instrução, são necessários alguns poucos números de instruções e alguns modos de endereçamento.

The Disadvantages of RISC architecture

- Mais, o desempenho dos processadores RISC depende do programador ou compilador, uma vez que o conhecimento do compilador desempenha um papel vital ao mesmo tempo que muda o código CISC para um código RISC

- enquanto que rearranjar o código CISC para um código RISC, denominado como uma expansão de código, aumentará o tamanho. E, a qualidade desta expansão de código dependerá novamente do compilador, e também do conjunto de instruções da máquina.

- O primeiro nível de cache dos processadores RISC é também uma desvantagem do RISC, no qual estes processadores têm grandes caches de memória no próprio chip. Para alimentar as instruções, requerem sistemas de memória muito rápidos.

Vantagens da arquitectura CISC

- A microprogramação é uma linguagem de montagem fácil de implementar, e menos dispendiosa do que a cablagem dura de uma unidade de controlo.

- A facilidade de microcodificação de novas instruções permitiu aos projectistas tornar as máquinas CISC compatíveis ascendentemente:

- A medida que cada instrução se tornava mais cumprida, menos instruções podiam ser usadas para implementar uma dada tarefa.

Desvantagens da arquitectura CISC

- O desempenho da máquina abranda devido à quantidade de O tempo de relógio tomado por diferentes instruções será diferente

- Apenas 20% das instruções existentes são utilizadas num evento de programação típico, embora haja várias instruções especializadas na realidade que nem sequer são utilizadas com frequência.

- Os códigos condicionais são definidos pelas instruções da CISC como um efeito secundário de cada instrução que leva tempo para esta definição – e, como a instrução subsequente altera os bits do código de condição – por isso, o compilador tem de examinar os bits do código de condição antes que isto aconteça.

Então, este artigo discute sobre as arquitecturas RISC e CISC; características da arquitectura do processador RISC e CISC; vantagens e desvantagens do RISC e CISC, e comparação entre as arquitecturas RISC e CISC . Para mais informações sobre as arquitecturas RISC e CISC, ou projectos eléctricos e electrónicos, por favor visite o link www.edgefxkits.com. Aqui está uma pergunta para si, quais são os últimos processadores da RISC e CISC?

Photo Credits:

- CISc e RISC Design by dickinson

- RISC Vs CISC by ydcdn

- CISC architecture by editsworld