What is RISC and CISC Architecture with Advantages and Disadvantages

CISC i RISC

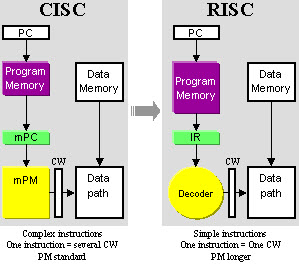

Architektura Centralnej Jednostki Przetwarzania działa zdolność do pracy z „Instruction Set Architecture” do miejsca, w którym została zaprojektowana. Architektoniczne projekty CPU to RISC (Reduced instruction set computing) i CISC (Complex instruction set computing). CISC ma zdolność do wykonywania trybów adresowania lub operacji wieloetapowych w ramach jednego zestawu instrukcji. Jest to konstrukcja procesora, w której jedna instrukcja wykonuje wiele operacji niskiego poziomu. Na przykład, przechowywanie w pamięci, operację arytmetyczną i ładowanie z pamięci. RISC to strategia projektowania procesora oparta na założeniu, że uproszczony zestaw instrukcji daje większą wydajność w połączeniu z architekturą mikroprocesora, która ma zdolność wykonywania instrukcji przy użyciu kilku cykli mikroprocesora na instrukcję.

Ten artykuł omawia architekturę RISC i CISC z odpowiednimi diagramami.

- Sprzęt firmy Intel jest określany jako Complex Instruction Set Computer (CISC)

- Sprzęt firmy Apple jest Reduced Instruction Set Computer (RISC).

Co to jest architektura RISC i CISC

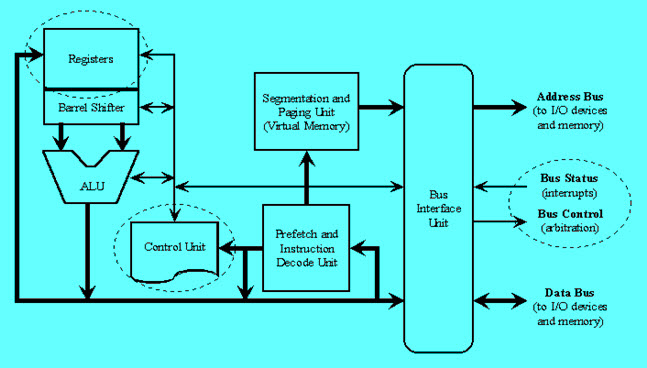

Projektanci sprzętu komputerowego wymyślają liczne technologie &narzędzia do implementacji pożądanej architektury w celu spełnienia tych potrzeb. Architektura sprzętowa może być realizowana jako specyficzna dla sprzętu lub specyficzna dla oprogramowania, ale w zależności od zastosowania obie są używane w wymaganej ilości. Jeśli chodzi o sprzęt procesora, istnieją 2 rodzaje koncepcji do wdrożenia architektury sprzętowej procesora. Pierwszą z nich jest RISC, a drugą CISC.

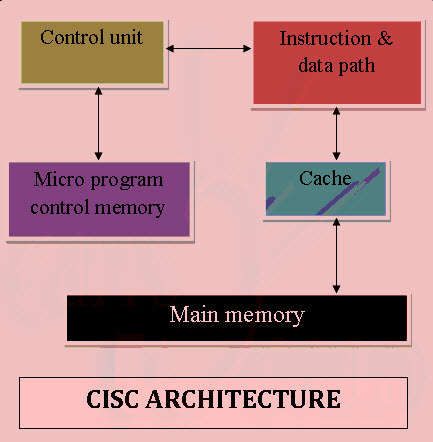

Architektura CISC

Podejście CISC próbuje zminimalizować liczbę instrukcji na program, poświęcając liczbę cykli na instrukcję. Komputery oparte na architekturze CISC są zaprojektowane w celu zmniejszenia kosztów pamięci. Ponieważ, duże programy potrzebują więcej pamięci, zwiększając w ten sposób koszt pamięci i duża pamięć staje się droższa. Aby rozwiązać te problemy, liczba instrukcji na program może być zmniejszona przez osadzenie liczby operacji w pojedynczej instrukcji, co czyni instrukcje bardziej złożonymi.

Architektura CISC

- MUL ładuje dwie wartości z pamięci do oddzielnych rejestrów w CISC.

- CISC używa minimalnej możliwej liczby instrukcji poprzez implementację sprzętową i wykonuje operacje.

- Architektura zestawu instrukcji jest medium umożliwiającym komunikację pomiędzy programistą a sprzętem. Część wykonawcza danych, kopiowanie danych, usuwanie lub edycja to polecenia użytkownika używane w mikroprocesorze i z tym mikroprocesorem współpracuje architektura zestawu instrukcji.

- Główne słowa kluczowe używane w powyższej architekturze zestawu instrukcji są następujące

Zestaw instrukcji: Grupa instrukcji podanych w celu wykonania programu i kierują komputerem poprzez manipulowanie danymi. Instrukcje mają postać – Opcode (kod operacyjny) i Operand. Gdzie, opcode jest instrukcją stosowaną do ładowania i przechowywania danych, itp. Operand jest rejestrem pamięci, w którym zastosowano instrukcję.

Tryby adresowania: Tryby adresowania to sposób, w jaki uzyskuje się dostęp do danych. W zależności od rodzaju zastosowanej instrukcji, tryby adresowania są różnego rodzaju, takie jak tryb bezpośredni, w którym uzyskuje się dostęp do prostych danych lub tryb pośredni, w którym uzyskuje się dostęp do lokalizacji danych. Procesory posiadające identyczny ISA mogą być bardzo różne w organizacji. Procesory z identycznym ISA i prawie identyczną organizacją nadal nie są prawie identyczne.

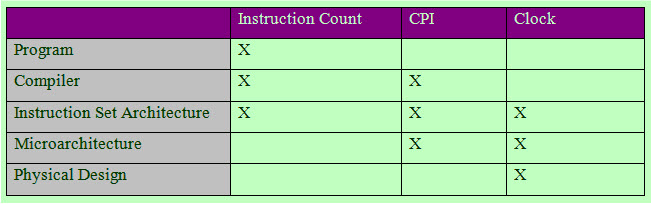

WydajnośćCPU jest dana przez podstawowe prawo

![]()

Tak więc, Wydajność procesora zależy od liczby instrukcji, CPI (cykli na instrukcję) i czasu cyklu zegara. A na wszystkie trzy wpływa architektura zestawu instrukcji.

Liczba instrukcji w procesorze

To podkreśla znaczenie architektury zestawu instrukcji. Istnieją dwie dominujące architektury zestawu instrukcji

Przykłady PROCESORÓW CISC

IBM 370/168 – Został wprowadzony w roku 1970. CISC projekt jest 32-bitowy procesor i cztery 64-bitowe rejestry zmiennoprzecinkowe.

VAX 11/780 – CISC projekt jest 32-bitowy procesor i obsługuje wiele numerów trybów adresowania i instrukcji maszynowych, który jest z Digital Equipment Corporation.

Intel 80486 – Został uruchomiony w roku 1989 i jest to procesor CISC, który ma instrukcje o różnej długości od 1 do 11 i będzie miał 235 instrukcji.

CHARAKTERYSTYKA ARCHITEKTURY CISC

- Logika dekodowania instrukcji będzie Złożona.

- Jedna instrukcja jest wymagana do obsługi wielu trybów adresowania.

- Mniej miejsca na chipie wystarczy na rejestry ogólnego przeznaczenia dla instrukcji, które są 0operowane bezpośrednio na pamięci.

- Różne projekty CISC mają ustawione dwa specjalne rejestry dla wskaźnika stosu, obsługi przerwań itp.

- MUL jest określany jako „złożona instrukcja” i wymaga programisty do przechowywania funkcji.

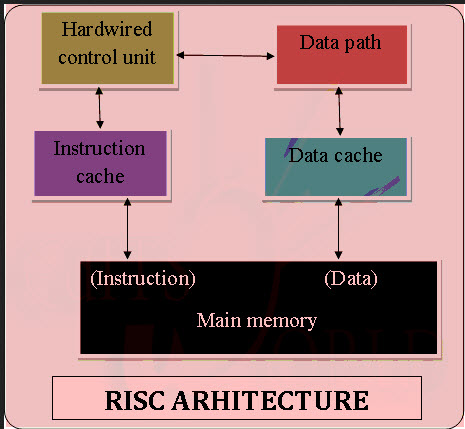

Architektura RISC

RISC (Reduced Instruction Set Computer) jest używany w urządzeniach przenośnych ze względu na jego wydajność energetyczną. Na przykład, Apple iPod i Nintendo DS. RISC to typ architektury mikroprocesora, który wykorzystuje wysoce zoptymalizowany zestaw instrukcji. RISC robi coś odwrotnego, redukując cykle na instrukcję kosztem liczby instrukcji w programie Pipelining jest jedną z unikalnych cech RISC. Jest ona wykonywana przez nakładanie na siebie wykonywania kilku instrukcji w sposób potokowy. Ma on dużą przewagę wydajnościową nad CISC.

Architektura RISC

Procesory RISC. przyjmują proste instrukcje i są wykonywane w cyklu zegarowym

KARTA ARCHITEKTURY RISC

- W architekturze RISC stosowane są proste instrukcje.

- RISC pomaga i obsługuje kilka prostych typów danych i syntetyzuje złożone typy danych.

- RISC wykorzystuje proste tryby adresowania i instrukcje o stałej długości dla pipeliningu.

- RISC pozwala na użycie dowolnego rejestru w dowolnym kontekście.

- Jednocyklowy czas wykonania

- Ilość pracy, którą może wykonać komputer jest zredukowana poprzez rozdzielenie instrukcji „LOAD” i „STORE”.

- RISC zawiera dużą liczbę rejestrów, aby zapobiec różnej liczbie interakcji z pamięcią.

- W RISC, Pipelining jest łatwy, ponieważ wykonanie wszystkich instrukcji zostanie wykonane w jednolitym przedziale czasu, tj. jedno kliknięcie.

- W RISC, więcej pamięci RAM jest wymagane do przechowywania instrukcji poziomu zespołu.

- Zmniejszona liczba instrukcji wymaga mniejszej liczby tranzystorów w RISC.

- RISC używa modelu pamięci Harvard, co oznacza, że jest to architektura Harvard.

- Kompilator służy do wykonywania operacji konwersji, czyli przekształcania wypowiedzi w języku wysokiego poziomu na kod w jego postaci.

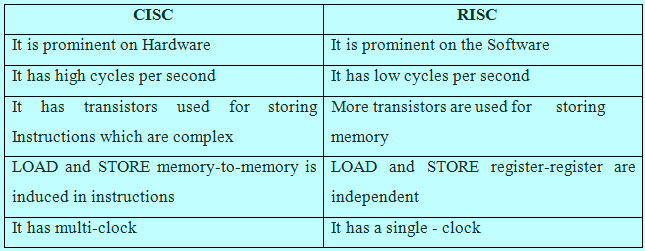

RISC & Porównanie CISC

Porównanie między CISC & RISC

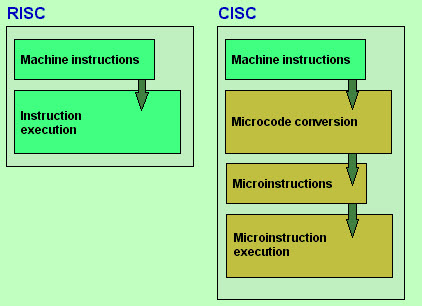

Instrukcja MUL dzieli się na trzy instrukcje

„LOAD” – przenosi dane z banku pamięci do rejestru

„PROD” – znajduje iloczyn dwóch operandów znajdujących się w rejestrach

„STORE” – przenosi dane z rejestru do banków pamięci

Główną różnicą między RISC a CISC jest liczba instrukcji i ich złożoność.

RISC Vs CISC

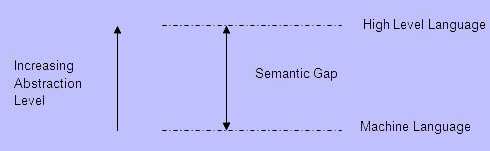

Lukę semantyczną

Obie architektury RISC i CISC zostały opracowane jako próba pokrycia luki semantycznej.

Lukę semantyczną

Mając na celu poprawę efektywności tworzenia oprogramowania, pojawiło się kilka potężnych języków programowania, viz, Ada, C, C++, Java, itp. Zapewniają one wysoki poziom abstrakcji, zwięzłości i mocy. W wyniku tej ewolucji rośnie luka semantyczna. Aby umożliwić wydajną kompilację programów w językach wysokiego poziomu, projekty CISC i RISC to dwie opcje.

Projekty CISC obejmują bardzo złożone architektury, w tym dużą liczbę instrukcji i trybów adresowania, podczas gdy projekty RISC obejmują uproszczony zestaw instrukcji i dostosowują go do rzeczywistych wymagań programów użytkownika.

CISC i RISC Design

Multiplikacja dwóch liczb w pamięci

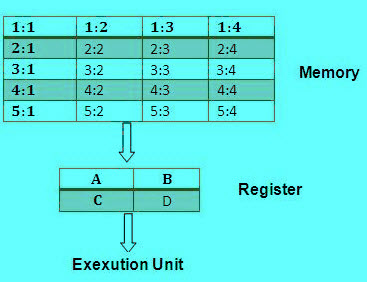

Jeśli pamięć główna jest podzielona na obszary, które są ponumerowane od wiersza1:kolumna 1 do wiersza 5 :kolumna 4. Dane są ładowane do jednego z czterech rejestrów (A, B, C lub D). Aby znaleźć mnożenie dwóch liczb – jednej przechowywanej w lokalizacji 1:3 i drugiej przechowywanej w lokalizacji 4:2 i zapisać wynik z powrotem w 1:3.

Multiplikacja dwóch liczb

Zalety i wady RISC i CISC

Zalety architektury RISC

- Architektura RISC(Reduced instruction set computing)posiada zestaw instrukcji, dzięki czemu kompilatory języków wysokiego poziomu mogą produkować bardziej wydajny kod

- Pozwala na swobodne wykorzystanie przestrzeni na mikroprocesorach ze względu na swoją prostotę.

- Wiele procesorów RISC używa rejestrów do przekazywania argumentów i trzymania zmiennych lokalnych.

- Funkcje RISC używają tylko kilku parametrów, a procesory RISC nie mogą używać instrukcji wywołania, a zatem używają instrukcji o stałej długości, która jest łatwa do pipeline.

- Szybkość działania może być zmaksymalizowana, a czas wykonania może być zminimalizowany.

Bardzo mniejsza liczba formatów instrukcji, kilka liczb instrukcji i kilka trybów adresowania są potrzebne.

Wady architektury RISC

- Najczęściej, wydajność procesorów RISC zależy od programisty lub kompilatora, ponieważ wiedza kompilatora odgrywa istotną rolę podczas zmiany kodu CISC na kod RISC

- Podczas zmiany układu kodu CISC na kod RISC, określany jako rozszerzenie kodu, zwiększy rozmiar. I, jakość tego rozszerzenia kodu będzie ponownie zależała od kompilatora, a także od zestawu instrukcji maszyny.

- Pierwszy poziom pamięci podręcznej procesorów RISC jest również wadą RISC, w którym te procesory mają duże pamięci podręczne na samym chipie. Do podawania instrukcji wymagają one bardzo szybkich systemów pamięci.

Wady architektury CISC

- Mikroprogramowanie jest łatwe do wdrożenia w języku montażu i mniej kosztowne niż twarde okablowanie jednostki sterującej.

- Łatwość mikrokodowania nowych instrukcji pozwoliła projektantom na uczynienie maszyn CISC kompatybilnymi w górę:

- Ponieważ każda instrukcja stała się bardziej dopracowana, mniej instrukcji można było użyć do wykonania danego zadania.

Wady architektury CISC

- Wydajność maszyny zwalnia z powodu ilości czasu zegara zajętego przez różne instrukcje będzie różna

- Tylko 20% istniejących instrukcji jest używanych w typowym zdarzeniu programistycznym, nawet jeśli w rzeczywistości istnieją różne wyspecjalizowane instrukcje, które nie są nawet często używane.

- Kody warunkowe są ustawiane przez instrukcje CISC jako efekt uboczny każdej instrukcji, która zajmuje czas na to ustawienie – i, ponieważ kolejna instrukcja zmienia bity kodu warunkowego – więc, kompilator musi zbadać bity kodu warunkowego, zanim to się stanie.

Ten artykuł omawia architektury RISC i CISC; cechy architektury procesora RISC i CISC; zalety i wady RISC i CISC, a także porównanie architektur RISC i CISC . Więcej informacji na temat architektur RISC i CISC lub projektów elektrycznych i elektronicznych można znaleźć na stronie www.edgefxkits.com. Oto pytanie dla Ciebie, jakie są najnowsze procesory RISC i CISC?

Photo Credits:

- CISc and RISC Design by dickinson

- RISC Vs CISC by ydcdn

- CISC architecture by editsworld