Wat is RISC en CISC Architectuur met Voor- en Nadelen

CISC en RISC

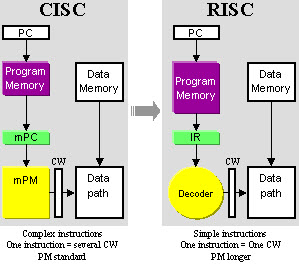

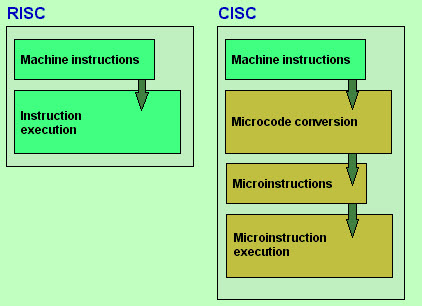

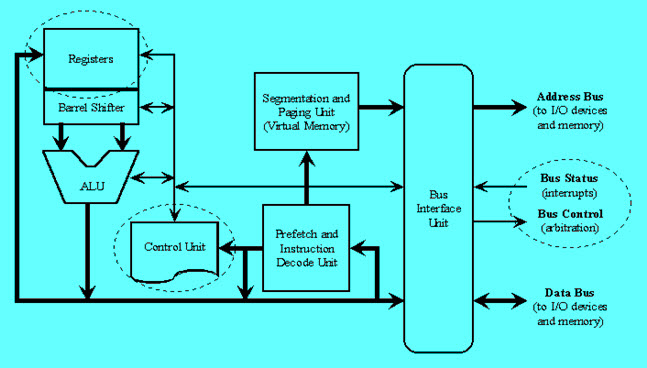

De architectuur van de centrale verwerkingseenheid werkt met de capaciteit om te werken vanuit de “Instructiesetarchitectuur” op de plaats waar hij is ontworpen. De architectonische ontwerpen van CPU zijn RISC (Reduced instruction set computing) en CISC (Complex instruction set computing). CISC heeft de mogelijkheid om adresseringsmodi of meerstapsbewerkingen uit te voeren binnen één instructieset. Het is het ontwerp van de CPU waarbij één instructie vele bewerkingen op laag niveau uitvoert. Bijvoorbeeld geheugenopslag, een rekenkundige bewerking en laden uit het geheugen. RISC is een CPU-ontwerpstrategie die is gebaseerd op het inzicht dat een vereenvoudigde instructieset hogere prestaties geeft wanneer deze wordt gecombineerd met een microprocessorarchitectuur die de mogelijkheid heeft de instructies uit te voeren met gebruikmaking van enkele microprocessorcycli per instructie.

Dit artikel bespreekt de RISC- en de CISC-architectuur met passende schema’s.

- Hardware van Intel wordt aangeduid als Complex Instruction Set Computer (CISC)

- Apple-hardware is Reduced Instruction Set Computer (RISC).

Wat is RISC- en CISC-architectuur

Hardware-ontwerpers vinden talrijke technologieën uit & hulpmiddelen om de gewenste architectuur te implementeren om aan deze behoeften te voldoen. Hardware-architectuur kan hardwarespecifiek of softwarespecifiek worden uitgevoerd, maar afhankelijk van de toepassing worden beide in de vereiste hoeveelheid gebruikt. Wat de processorhardware betreft, zijn er 2 soorten concepten om de processorhardware-architectuur te implementeren. De eerste is RISC en de andere is CISC.

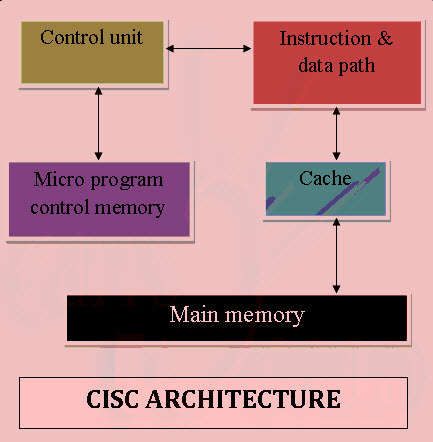

CISC-architectuur

De CISC-benadering tracht het aantal instructies per programma te minimaliseren, waarbij het aantal cycli per instructie wordt opgeofferd. Computers op basis van de CISC-architectuur zijn ontworpen om de geheugenkosten te verminderen. Want grote programma’s hebben meer opslagruimte nodig, waardoor de geheugenkosten toenemen en groot geheugen duurder wordt. Om deze problemen op te lossen, kan het aantal instructies per programma worden verminderd door het aantal bewerkingen in één enkele instructie onder te brengen, waardoor de instructies complexer worden.

CISC-architectuur

- MUL laadt in CISC twee waarden uit het geheugen in afzonderlijke registers.

- CISC gebruikt zo min mogelijk instructies door hardware te implementeren en voert bewerkingen uit.

- Instruction Set Architecture is een medium om communicatie tussen de programmeur en de hardware mogelijk te maken. Het uitvoeren van gegevens, het kopiëren van gegevens, het wissen of bewerken zijn de gebruikerscommando’s die in de microprocessor worden gebruikt en met deze microprocessor wordt de Instructieset-architectuur bediend.

- De belangrijkste trefwoorden die in de bovengenoemde Instructieset-architectuur worden gebruikt, zijn als volgt

Instructieset: Groep instructies die wordt gegeven om het programma uit te voeren en zij sturen de computer door het manipuleren van de gegevens. Instructies hebben de vorm – Opcode (operationele code) en Operand. Waar, opcode de instructie is die wordt toegepast om gegevens te laden en op te slaan, enz. De operand is een geheugenregister waar de instructie wordt toegepast.

Adresseringsmodi: Adresseringsmodi zijn de manier waarop de gegevens worden benaderd. Afhankelijk van het type instructie dat wordt toegepast, zijn er verschillende adresseringsmodi, zoals directe modus, waarbij de gegevens rechtstreeks worden benaderd, of indirecte modus, waarbij de locatie van de gegevens wordt benaderd. Processoren met een identieke ISA kunnen zeer verschillend zijn qua organisatie. Processoren met een identieke ISA en een bijna identieke organisatie zijn nog steeds niet bijna identiek.

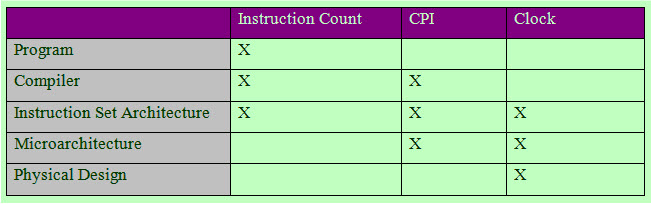

CPU-prestaties worden gegeven door de fundamentele wet

![]()

Dus, CPU-prestaties zijn afhankelijk van het aantal instructies, de CPI (cycli per instructie) en de klokcyclustijd. En alle drie worden beïnvloed door de instructieset-architectuur.

Instructietelling van de CPU

Dit onderstreept het belang van de instructieset-architectuur. Er zijn twee gangbare instructieset-architecturen

Voorbeelden van CISC PROCESSOREN

IBM 370/168 – Deze werd geïntroduceerd in het jaar 1970. CISC-ontwerp is een 32-bit processor en vier 64-bit floating point registers.

VAX 11/780 – CISC-ontwerp is een 32-bit processor en ondersteunt een groot aantal adresseringsmodi en machine-instructies, die afkomstig zijn van Digital Equipment Corporation.

Intel 80486 – Deze werd gelanceerd in het jaar 1989 en het is een CISC processor, die instructies heeft variërend in lengte van 1 tot 11 en hij zal 235 instructies hebben.

CHARACTERISTIEKEN VAN DE CISC ARCHITECTUUR

- Instructie-decoderingslogica zal Complex zijn.

- Een instructie is nodig om meerdere adresseringsmodi te ondersteunen.

- Er is minder chipruimte nodig voor algemene registers voor de instructies die direct op het geheugen worden uitgevoerd.

- Verschillende CISC-ontwerpen hebben twee speciale registers voor de stack pointer, het afhandelen van interrupts, enz.

- MUL wordt een “complexe instructie” genoemd en vereist de programmeur voor het opslaan van functies.

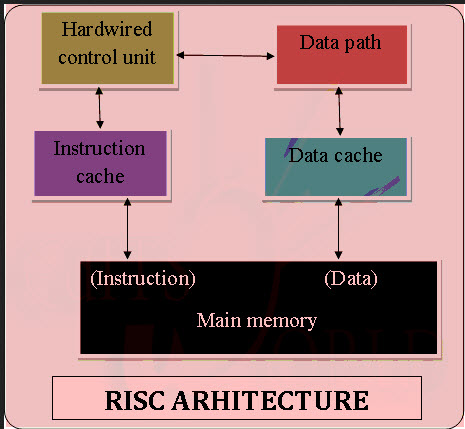

RISC Architectuur

RISC (Reduced Instruction Set Computer) wordt gebruikt in draagbare apparaten vanwege zijn energie-efficiëntie. Bijvoorbeeld, Apple iPod en Nintendo DS. RISC is een type microprocessorarchitectuur die gebruik maakt van een sterk geoptimaliseerde set instructies. RISC doet het tegenovergestelde, de cycli per instructie verminderen ten koste van het aantal instructies per programma Pipelining is een van de unieke kenmerken van RISC. Het wordt uitgevoerd door de uitvoering van verschillende instructies in een pijplijn te overlappen. Het biedt een groot prestatievoordeel ten opzichte van CISC.

RISC-architectuur

RISC-processoren nemen eenvoudige instructies aan en worden binnen een klokcyclus uitgevoerd

RISC-ARCHITECTUURKENMERKEN

- Eenvoudige instructies worden gebruikt in de RISC-architectuur.

- RISC helpt en ondersteunt weinig eenvoudige gegevenstypen en synthetiseert complexe gegevenstypen.

- RISC maakt gebruik van eenvoudige adresseringsmodi en instructies met vaste lengte voor pipelining.

- RISC staat toe elk register in elke context te gebruiken.

- Uitvoeringstijd van één cyclus

- De hoeveelheid werk die een computer kan verrichten wordt verminderd door “LOAD” en “STORE” instructies van elkaar te scheiden.

- RISC bevat een groot aantal registers om diverse interacties met het geheugen te voorkomen.

- In RISC is Pipelining gemakkelijk omdat de uitvoering van alle instructies in een uniform tijdsinterval, d.w.z. één klik, plaatsvindt.

- In RISC is meer RAM nodig om assemblage-instructies op te slaan.

- Minder instructies hebben in RISC minder transistors nodig.

- RISC gebruikt Harvard-geheugenmodel betekent dat het Harvard-architectuur is.

- Een compiler wordt gebruikt om de conversie uit te voeren, d.w.z. om een verklaring in een taal op hoog niveau om te zetten in de code van zijn vorm.

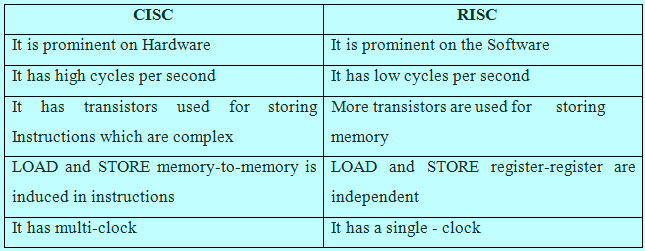

RISC & CISC Vergelijking

Vergelijking tussen CISC & RISC

MUL-instructie is onderverdeeld in drie instructies

“LOAD” – verplaatst gegevens van de geheugenbank naar een register

“PROD” – vindt het product van twee operanden die zich in de registers bevinden

“STORE” – verplaatst gegevens van een register naar de geheugenbanken

Het belangrijkste verschil tussen RISC en CISC is het aantal instructies en de complexiteit ervan.

RISC Vs CISC

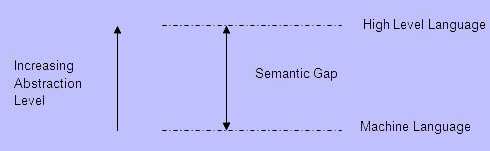

SEMANTISCHE GAP

Zowel RISC- als CISC-architecturen zijn ontwikkeld in een poging de semantische kloof te overbruggen.

Semantische kloof

Met als doel de efficiëntie van software-ontwikkeling te verbeteren, zijn er verschillende krachtige programmeertalen ontstaan, nl, Ada, C, C++, Java, enz. Zij bieden een hoog niveau van abstractie, beknoptheid en kracht. Door deze evolutie groeit de semantische kloof. Om efficiënte compilatie van programma’s op hoog niveau mogelijk te maken, zijn CISC- en RISC-ontwerpen de twee opties.

CISC-ontwerpen omvatten zeer complexe architecturen, met inbegrip van een groot aantal instructies en adresseringsmodi, terwijl RISC-ontwerpen vereenvoudigde instructiesets omvatten en deze aanpassen aan de werkelijke eisen van gebruikersprogramma’s.

CISC- en RISC-ontwerpen

Vermenigvuldiging van twee Getallen in Geheugen

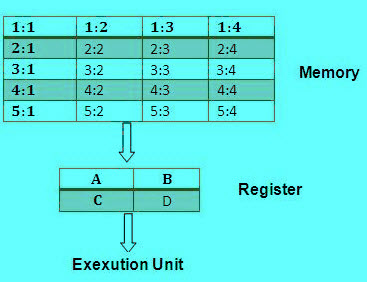

Als het hoofdgeheugen is verdeeld in gebieden die genummerd zijn van rij1:kolom 1 tot rij 5 :kolom 4. De gegevens worden in een van de vier registers (A, B, C of D) geladen. Om de vermenigvuldiging van twee getallen te vinden – één opgeslagen op plaats 1:3 en het andere opgeslagen op plaats 4:2 en het resultaat op te slaan in 1:3.

Vermenigvuldiging van twee getallen

De voor- en nadelen van RISC en CISC

De voordelen van de RISC-architectuur

- RISC(Reduced instruction set computing)-architectuur heeft een set instructies, zodat high-level taalcompilers efficiëntere code kunnen produceren

- Het laat vrijheid van gebruik van de ruimte op microprocessoren toe vanwege zijn eenvoud.

- Veel RISC-processoren gebruiken de registers voor het doorgeven van argumenten en het vasthouden van de lokale variabelen.

- RISC functies gebruiken slechts een paar parameters, en de RISC processoren kunnen de call instructies niet gebruiken, en gebruiken daarom een instructie met vaste lengte die gemakkelijk te pijplijnen is.

- De snelheid van de bewerking kan worden gemaximaliseerd en de uitvoeringstijd kan worden geminimaliseerd.

Zeer weinig instructie-formaten, een paar aantallen instructies en een paar adresseringswijzen zijn nodig.

De nadelen van de RISC architectuur

- Meestal, hangt de prestatie van de RISC-processoren af van de programmeur of de compiler, omdat de kennis van de compiler een vitale rol speelt bij het veranderen van de CISC-code in een RISC-code

- Bij het herschikken van de CISC-code in een RISC-code, aangeduid als code-uitbreiding, neemt de omvang toe. En, de kwaliteit van deze code uitbreiding zal weer afhangen van de compiler, en ook van de instructieset van de machine.

- De first level cache van de RISC processoren is ook een nadeel van de RISC, waarbij deze processoren grote geheugen caches op de chip zelf hebben. Voor het voeden van de instructies hebben ze zeer snelle geheugensystemen nodig.

Voordelen van de CISC-architectuur

- Microprogrammering is eenvoudig in assembleertaal uit te voeren, en minder duur dan het hard bedraden van een besturingseenheid.

- Het gemak van microcodering van nieuwe instructies stelde ontwerpers in staat CISC-machines opwaarts compatibel te maken:

- Naarmate elke instructie meer werd uitgevoerd, konden minder instructies worden gebruikt om een bepaalde taak uit te voeren.

Nadelen van CISC-architectuur

- De prestaties van de machine worden trager doordat de hoeveelheid kloktijd die de verschillende instructies in beslag nemen

- Slechts 20% van de bestaande instructies wordt gebruikt in een typische programmering, ook al zijn er in werkelijkheid diverse gespecialiseerde instructies die niet eens vaak worden gebruikt.

- De voorwaardelijke codes worden door de CISC-instructies ingesteld als neveneffect van elke instructie, hetgeen tijd kost voor dit instellen – en, omdat de daaropvolgende instructie de conditiecode-bits verandert – moet de compiler dus de conditiecode-bits onderzoeken voordat dit gebeurt.

Dit artikel gaat over de RISC- en CISC-architecturen; kenmerken van de RISC- en CISC-processorarchitectuur; voor- en nadelen van RISC en CISC, en vergelijking tussen de RISC- en CISC-architecturen. Voor meer informatie over de RISC- en CISC-architecturen, of over elektrische en elektronische projecten, kunt u de link www.edgefxkits.com bezoeken. Hier is een vraag voor u, wat zijn de nieuwste RISC- en CISC-processoren?

Photo Credits:

- CISc en RISC Design door dickinson

- RISC Vs CISC door ydcdn

- CISC architectuur door editsworld