Qué es la arquitectura RISC y CISC con sus ventajas y desventajas

CISC y RISC

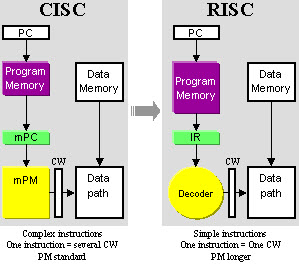

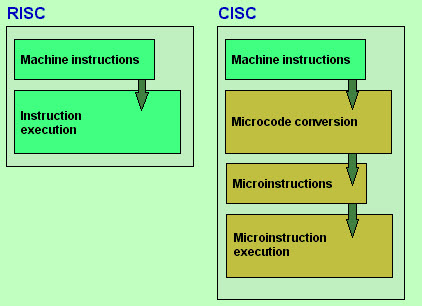

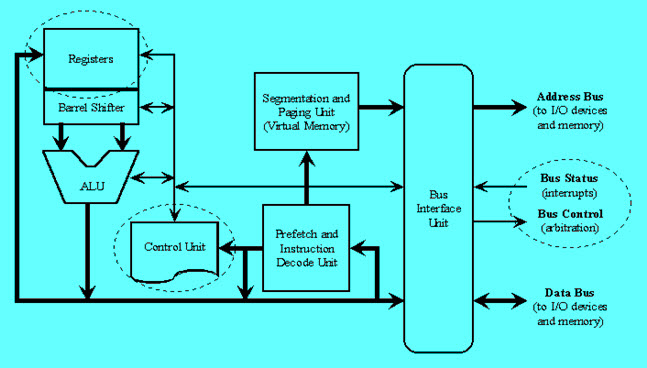

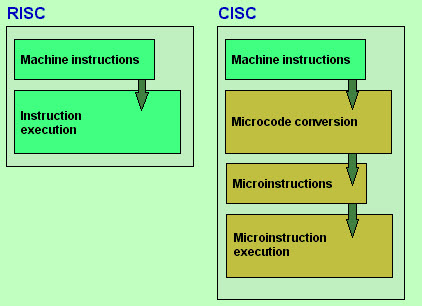

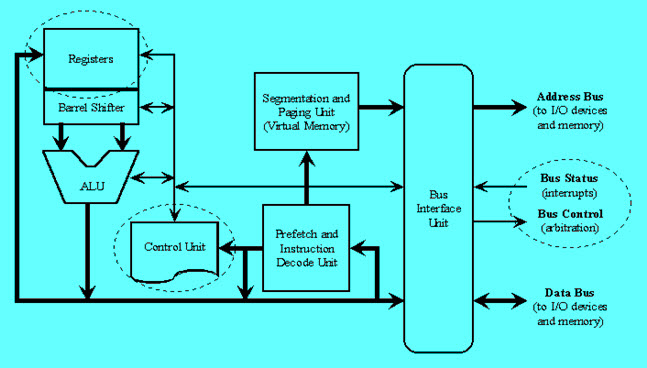

La Arquitectura de la Unidad Central de Procesamiento opera la capacidad de trabajar desde la «Arquitectura del Conjunto de Instrucciones» hasta donde fue diseñada. Los diseños arquitectónicos de CPU son RISC (Reduced instruction set computing) y CISC (Complex instruction set computing). CISC tiene la capacidad de ejecutar modos de direccionamiento u operaciones de varios pasos dentro de un conjunto de instrucciones. Es el diseño de la CPU en el que una instrucción realiza muchas operaciones de bajo nivel. Por ejemplo, el almacenamiento en memoria, una operación aritmética y la carga desde la memoria. RISC es una estrategia de diseño de la CPU basada en la idea de que un conjunto de instrucciones simplificado proporciona un mayor rendimiento cuando se combina con una arquitectura de microprocesador que tiene la capacidad de ejecutar las instrucciones utilizando algunos ciclos de microprocesador por instrucción.

Este artículo trata sobre la arquitectura RISC y CISC con diagramas adecuados.

- El hardware de Intel se denomina Complex Instruction Set Computer (CISC)

- El hardware de Apple es Reduced Instruction Set Computer (RISC).

Qué es la arquitectura RISC y CISC

Los diseñadores de hardware inventan numerosas tecnologías & herramientas para implementar la arquitectura deseada con el fin de satisfacer estas necesidades. La arquitectura de hardware puede implementarse para ser específica de hardware o específica de software, pero según la aplicación se utilizan ambas en la cantidad requerida. En lo que respecta al hardware del procesador, existen dos tipos de conceptos para implementar la arquitectura de hardware del procesador. El primero es RISC y el otro es CISC.

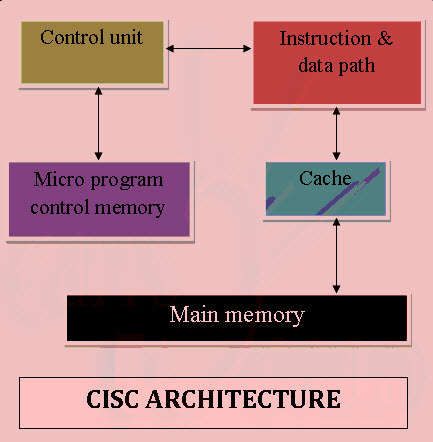

Arquitectura CISC

El enfoque CISC intenta minimizar el número de instrucciones por programa, sacrificando el número de ciclos por instrucción. Los ordenadores basados en la arquitectura CISC están diseñados para disminuir el coste de la memoria. Porque, los programas grandes necesitan más almacenamiento, aumentando así el coste de la memoria y la memoria grande se vuelve más cara. Para solucionar estos problemas, se puede reducir el número de instrucciones por programa incrustando el número de operaciones en una sola instrucción, haciendo así las instrucciones más complejas.

Arquitectura CISC

- MUL carga dos valores de la memoria en registros separados en CISC.

- CISC utiliza el mínimo de instrucciones posibles al implementar el hardware y ejecuta las operaciones.

- La arquitectura de conjuntos de instrucciones es un medio que permite la comunicación entre el programador y el hardware. La parte de ejecución de datos, la copia de datos, el borrado o la edición son los comandos de usuario utilizados en el microprocesador y con este microprocesador se opera la arquitectura del conjunto de instrucciones.

- Las principales palabras clave utilizadas en la arquitectura del conjunto de instrucciones anterior son las siguientes

- La lógica de decodificación de instrucciones será Compleja.

- Se requiere una instrucción para soportar múltiples modos de direccionamiento.

- Se dispone de menos espacio en el chip para los registros de propósito general para las instrucciones que se 0peran directamente en la memoria.

- En varios diseños CISC se establecen dos registros especiales para el puntero de la pila, el manejo de las interrupciones, etc.

- MUL se denomina «instrucción compleja» y requiere del programador para almacenar funciones.

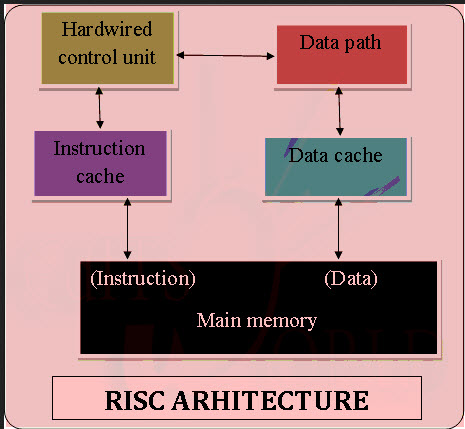

- En la arquitectura RISC se utilizan instrucciones simples.

- RISC ayuda y soporta pocos tipos de datos simples y sintetiza tipos de datos complejos.

- RISC utiliza modos de direccionamiento simples e instrucciones de longitud fija para el pipelining.

- RISC permite utilizar cualquier registro en cualquier contexto.

- Tiempo de ejecución de un ciclo

- La cantidad de trabajo que puede realizar un ordenador se reduce al separar las instrucciones «LOAD» y «STORE».

- RISC contiene un gran número de registros con el fin de evitar varios números de interacciones con la memoria.

- En RISC, el Pipelining es fácil ya que la ejecución de todas las instrucciones se realizará en un intervalo de tiempo uniforme, es decir, un clic.

- En RISC, se requiere más RAM para almacenar las instrucciones de nivel de ensamblaje.

- Las instrucciones reducidas necesitan un menor número de transistores en RISC.

- RISC utiliza el modelo de memoria Harvard significa que es la Arquitectura Harvard.

- Un compilador se utiliza para realizar la operación de conversión significa convertir una declaración de lenguaje de alto nivel en el código de su forma.

- La arquitectura RISC(Reduced instruction set computing)tiene un conjunto de instrucciones, por lo que los compiladores de lenguaje de alto nivel pueden producir un código más eficiente

- Permite libertad de uso del espacio en los microprocesadores debido a su simplicidad.

- Muchos procesadores RISC utilizan los registros para pasar argumentos y mantener las variables locales.

- Las funciones RISC utilizan sólo unos pocos parámetros, y los procesadores RISC no pueden utilizar las instrucciones de llamada, y por lo tanto, utilizan una instrucción de longitud fija que es fácil de canalizar.

- Se puede maximizar la velocidad de la operación y minimizar el tiempo de ejecución.

Se necesita un número muy reducido de formatos de instrucción, un número reducido de instrucciones y unos pocos modos de direccionamiento. - La mayoría, el rendimiento de los procesadores RISC depende del programador o del compilador, ya que el conocimiento del compilador juega un papel vital mientras se cambia el código CISC a un código RISC

- Mientras se reordena el código CISC a un código RISC, denominado expansión de código, aumentará el tamaño. Y, la calidad de esta expansión de código dependerá de nuevo del compilador, y también del conjunto de instrucciones de la máquina.

- La caché de primer nivel de los procesadores RISC es también una desventaja de los RISC, en los que estos procesadores tienen grandes cachés de memoria en el propio chip. Para alimentar las instrucciones, requieren sistemas de memoria muy rápidos.

- La microprogramación es fácil de implementar en lenguaje ensamblador, y menos costosa que el cableado duro de una unidad de control.

- La facilidad de microcodificación de nuevas instrucciones permitió a los diseñadores hacer que las máquinas CISC fueran compatibles con el nivel superior:

- A medida que cada instrucción se hacía más completa, se podían utilizar menos instrucciones para implementar una tarea determinada.

- El rendimiento de la máquina se ralentiza debido a que la cantidad de tiempo de reloj que toman las diferentes instrucciones será disímil

- Sólo el 20% de las instrucciones existentes se utiliza en un evento típico de programación, aunque en la realidad hay varias instrucciones especializadas que ni siquiera se utilizan con frecuencia.

- Los códigos condicionales son establecidos por las instrucciones CISC como un efecto secundario de cada instrucción que toma tiempo para esta configuración – y, como la instrucción posterior cambia los bits del código de condición – por lo que, el compilador tiene que examinar los bits del código de condición antes de que esto ocurra.

- Diseño de RISC y RISC por dickinson

- RISC Vs CISC por ydcdn

- Arquitectura CISC por editsworld

Conjunto de instrucciones: Grupo de instrucciones dadas para ejecutar el programa y que dirigen al ordenador manipulando los datos. Las instrucciones tienen la forma – Opcode (código operacional) y Operand. Donde, opcode es la instrucción aplicada para cargar y almacenar datos, etc. El operando es un registro de memoria donde se aplica la instrucción.

Modos de direccionamiento: Los modos de direccionamiento son la forma en que se accede a los datos. Dependiendo del tipo de instrucción aplicada, los modos de direccionamiento son de varios tipos como el modo directo donde se accede a los datos directamente o el modo indirecto donde se accede a la ubicación de los datos. Los procesadores que tienen una ISA idéntica pueden ser muy diferentes en su organización. Los procesadores con idéntica ISA y casi idéntica organización aún no son casi idénticos.

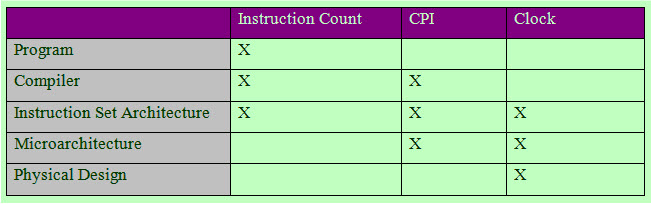

El rendimiento de la CPU viene dado por la ley fundamental

![]()

Así, El rendimiento de la CPU depende del recuento de instrucciones, del IPC (ciclos por instrucción) y del tiempo de ciclo del reloj. Y los tres se ven afectados por la arquitectura del conjunto de instrucciones.

Cuento de instrucciones de la CPU

Esto subraya la importancia de la arquitectura del conjunto de instrucciones. Hay dos arquitecturas de conjuntos de instrucciones prevalentes

Ejemplos de PROCESADORES CISC

IBM 370/168 – Se introdujo en el año 1970. El diseño CISC es un procesador de 32 bits y cuatro registros de punto flotante de 64 bits.

VAX 11/780 – El diseño CISC es un procesador de 32 bits y admite un gran número de modos de direccionamiento e instrucciones de máquina que es de Digital Equipment Corporation.

Intel 80486 – Fue lanzado en el año 1989 y es un procesador CISC, que tiene instrucciones de longitudes variables de 1 a 11 y tendrá 235 instrucciones.

CARACTERÍSTICAS DE LA ARQUITECTURA CISC

Arquitectura RISC

RISC (Reduced Instruction Set Computer) se utiliza en dispositivos portátiles debido a su eficiencia energética. Por ejemplo, el iPod de Apple y la Nintendo DS. RISC es un tipo de arquitectura de microprocesador que utiliza un conjunto de instrucciones altamente optimizado. RISC hace lo contrario, reducir los ciclos por instrucción a costa del número de instrucciones por programa El pipelining es una de las características únicas de RISC. Se realiza solapando la ejecución de varias instrucciones en forma de pipeline. Tiene una gran ventaja de rendimiento sobre CISC.

Arquitectura RISC

Los procesadores RISC toman instrucciones simples y se ejecutan en un ciclo de reloj

CARACTERÍSTICAS DE LA ARQUITECTURA RISC

RISC &

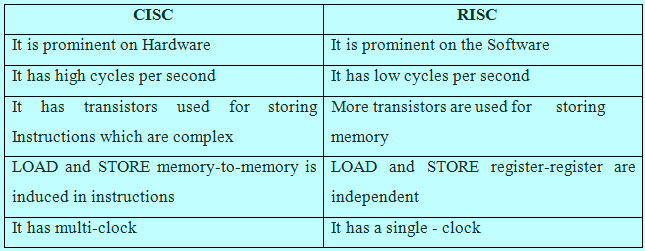

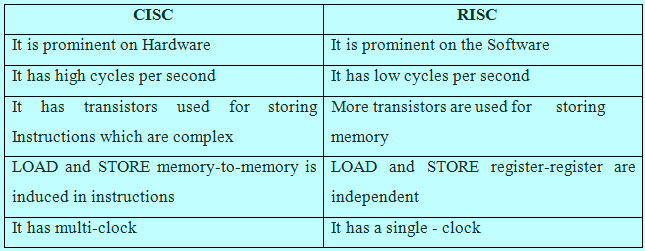

Comparación entre CISC & RISC

La instrucción MUL se divide en tres instrucciones

«LOAD» – mueve datos del banco de memoria a un registro

«PROD» – encuentra el producto de dos operandos situados dentro de los registros

«STORE» – mueve datos de un registro a los bancos de memoria

La principal diferencia entre RISC y CISC es el número de instrucciones y su complejidad.

RISC Vs CISC

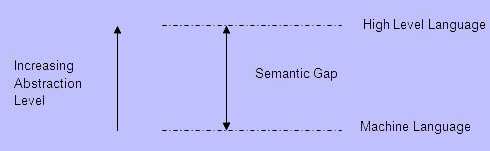

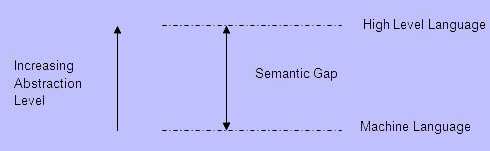

Gap semántico

Tanto las arquitecturas RISC como CISC se han desarrollado como un intento de cubrir el gap semántico.

La brecha semántica

Con el objetivo de mejorar la eficiencia del desarrollo de software, han surgido varios lenguajes de programación potentes, a saber, Ada, C, C++, Java, etc. Proporcionan un alto nivel de abstracción, concisión y potencia. Con esta evolución crece la brecha semántica. Para permitir la compilación eficiente de programas de lenguaje de alto nivel, los diseños CISC y RISC son las dos opciones.

Los diseños CISC implican arquitecturas muy complejas, que incluyen un gran número de instrucciones y modos de direccionamiento, mientras que los diseños RISC implican un conjunto de instrucciones simplificado y lo adaptan a los requisitos reales de los programas de usuario.

Diseño de CSI y RISC

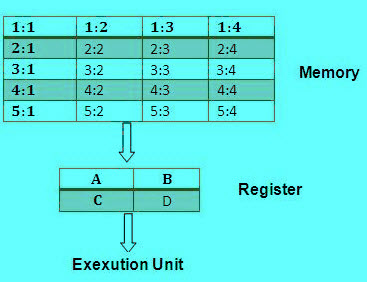

Multiplicación de dos Números en Memoria

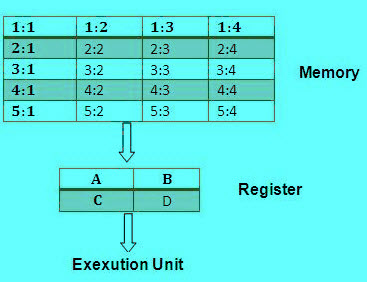

Si la memoria principal está dividida en áreas que se numeran desde la fila1:columna 1 a la fila 5 :columna 4. Los datos se cargan en uno de los cuatro registros (A, B, C o D). Para encontrar la multiplicación de dos números- Uno almacenado en la ubicación 1:3 y otro almacenado en la ubicación 4:2 y almacenar de nuevo el resultado en 1:3.

Multiplicación de dos números

Las ventajas y desventajas de RISC y CISC

Las ventajas de la arquitectura RISC

Las desventajas de la arquitectura RISC

Ventajas de la arquitectura CISC

Desventajas de la arquitectura CISC

Así pues, este artículo trata sobre las arquitecturas RISC y CISC; características de la arquitectura de los procesadores RISC y CISC; ventajas e inconvenientes de RISC y CISC, y comparación entre las arquitecturas RISC y CISC . Para obtener más información sobre las arquitecturas RISC y CISC, o sobre proyectos de electricidad y electrónica, visite el enlace www.edgefxkits.com. Aquí hay una pregunta para ti, ¿cuáles son los últimos procesadores RISC y CISC?

Créditos de las fotos:

Comparación entre CISC & RISC

«LOAD» – mueve datos del banco de memoria a un registro

«PROD» – encuentra el producto de dos operandos situados dentro de los registros

«STORE» – mueve datos de un registro a los bancos de memoria

La principal diferencia entre RISC y CISC es el número de instrucciones y su complejidad.

RISC Vs CISC

Gap semántico

Tanto las arquitecturas RISC como CISC se han desarrollado como un intento de cubrir el gap semántico.

La brecha semántica

Con el objetivo de mejorar la eficiencia del desarrollo de software, han surgido varios lenguajes de programación potentes, a saber, Ada, C, C++, Java, etc. Proporcionan un alto nivel de abstracción, concisión y potencia. Con esta evolución crece la brecha semántica. Para permitir la compilación eficiente de programas de lenguaje de alto nivel, los diseños CISC y RISC son las dos opciones.

Los diseños CISC implican arquitecturas muy complejas, que incluyen un gran número de instrucciones y modos de direccionamiento, mientras que los diseños RISC implican un conjunto de instrucciones simplificado y lo adaptan a los requisitos reales de los programas de usuario.

Diseño de CSI y RISC

Multiplicación de dos Números en Memoria

Si la memoria principal está dividida en áreas que se numeran desde la fila1:columna 1 a la fila 5 :columna 4. Los datos se cargan en uno de los cuatro registros (A, B, C o D). Para encontrar la multiplicación de dos números- Uno almacenado en la ubicación 1:3 y otro almacenado en la ubicación 4:2 y almacenar de nuevo el resultado en 1:3.

Multiplicación de dos números

Las ventajas y desventajas de RISC y CISC

Las ventajas de la arquitectura RISC

Las desventajas de la arquitectura RISC

Ventajas de la arquitectura CISC

Desventajas de la arquitectura CISC

Así pues, este artículo trata sobre las arquitecturas RISC y CISC; características de la arquitectura de los procesadores RISC y CISC; ventajas e inconvenientes de RISC y CISC, y comparación entre las arquitecturas RISC y CISC . Para obtener más información sobre las arquitecturas RISC y CISC, o sobre proyectos de electricidad y electrónica, visite el enlace www.edgefxkits.com. Aquí hay una pregunta para ti, ¿cuáles son los últimos procesadores RISC y CISC?

Créditos de las fotos: